University of Florida, EEL 4744 – File 00 © Dr. Eric M. Schwartz

1

© Dr. Eric M. Schwartz

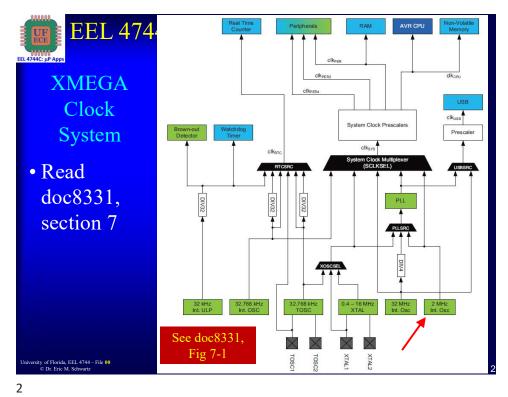

## EEL 4744 Configuration Change Protection (Changing the System Clock)

You can <u>not</u> allow interrupts while changing the system clock source and it must happen <u>fast</u>

Must write the appropriate value to the Configuration Change Protection (CCP) Register, CPU\_CCP (see doc 8331, section 3.14.1), to disable interrupts for a few clock cycles to give time to change the clock source

Ex: See include file and section 3.14.1 in doc8331

.equ CCP\_IOREG\_gc = (0xD8<<0); IO Register Protection 1di r16, CCP\_IOREG\_gc sts CPU\_CCP, r16</li>

After above, ready to immediately write to CLK\_CTRL

#### 6

University of Florida, EEL 4744 – File 00 © Dr. Eric M. Schwartz

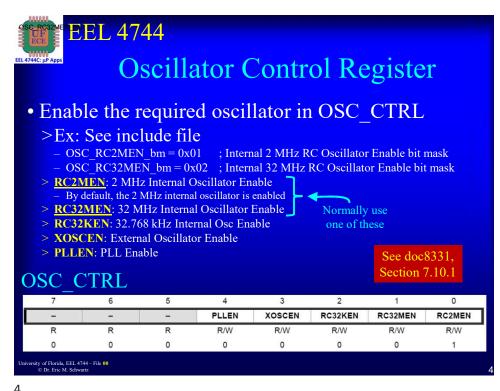

| See doc<br>Section                                                                                |        | '44<br>Cloc | k Co   | ntro     | ol Re          | gister          |                   |

|---------------------------------------------------------------------------------------------------|--------|-------------|--------|----------|----------------|-----------------|-------------------|

| <ul> <li>Store to CLK_CTRL to</li> </ul>                                                          |        |             |        |          | CLKSEL<br>[20] | Group<br>Config | Description       |

| change the system clock                                                                           |        |             |        |          | 000            | RC2MHZ          | 2MHz int osc      |

| >Ex: See include file                                                                             |        |             |        |          | 001            | RC32MHZ         | 32MHz int osc     |

| $- CLK_SCLKSEL_RC32M_gc = (0x01 << 0)$                                                            |        |             |        |          | 010            | RC2KHZ          | 32.768 int osc    |

| ; Internal 32 MHz RC Oscillator                                                                   |        |             |        |          | 011            | XOSC            | Ext osc           |

| <ul> <li>CLK_SCLKSEL_RC2M_gc = (0x00&lt;&lt;0)</li> <li>; Internal 2 MHz RC Oscillator</li> </ul> |        |             |        |          | 100            | PLL             | Phase locked loop |

|                                                                                                   |        | 101         |        | Reserved |                |                 |                   |

|                                                                                                   |        |             |        |          | 11-            |                 | Reserved          |

| CLK_C                                                                                             | TRL    |             |        |          |                |                 |                   |

| 7                                                                                                 | 6      | 5           | 4      | 3        | 2              |                 |                   |

| – –                                                                                               | -<br>R | - R         | -<br>R | -<br>R   | R/W            | SCLKSEL[2:0]    |                   |

| 0                                                                                                 | 0      | 0           | 0      | 0        | 0              | 0               | 0                 |

| University of Florida, EEL 47<br>© Dr. Eric M. Schwa                                              |        |             |        |          |                |                 | 7                 |

#### EEL 4744

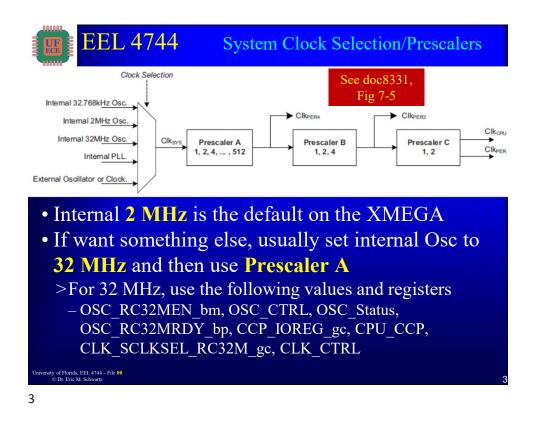

# Changing the System Clock

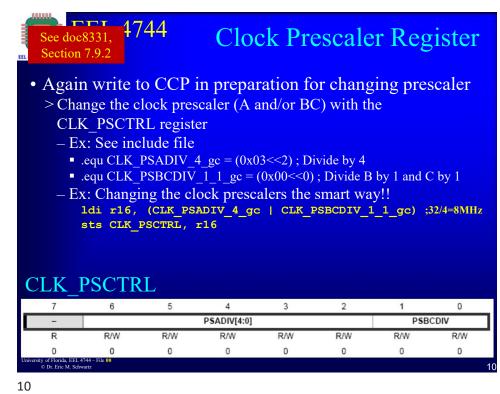

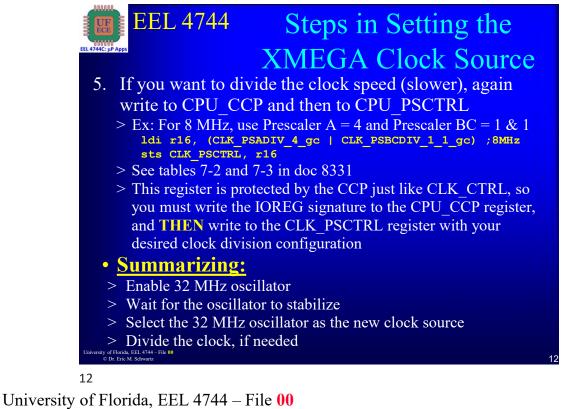

Once the clock is set to 32 MHz, you can change the system clock by using CLK\_PSCTRL along with CLK\_PSADIV\_x\_gc, CLK\_PSBCDIV\_y\_gc, where x is a power of 2 between 1 and 512 and y corresponds to a Prescaler B value and a Prescaler C value

Both Prescaler B & C (PSBC) divider values are usually 1: .equ CLK\_PSBCDIV\_1\_1\_gc = (0x00<<0) ; Divide B by 1 and C by 1</li>

For a Prescaler A divider value of 4 ATxmega128a1udef.inc .equ CLK\_PSADIV\_4\_gc = (0x03<<2) ; Divide by 4

<ul>

See doc8331, Table 7-2 (on next page)

#### 8

University of Florida, EEL 4744 – File 00 © Dr. Eric M. Schwartz

| HC: µP Apps                                    | EL 4<br>See doc8<br>Table 7 | 331,          | System          | ı Clo           | <b>ck Prescaler A</b><br>See doc8331,<br>Table 7-3 |                         |

|------------------------------------------------|-----------------------------|---------------|-----------------|-----------------|----------------------------------------------------|-------------------------|

| PSADIV<br>[40]                                 | Group<br>Config             | Description   | PSBCDIV[<br>10] | Group<br>Config | Prescaler B<br>division                            | Prescaler C<br>division |

| 0 0000                                         | 1                           | No division   | 00              | 1_1             | No division                                        | No division             |

| 0 0001                                         | 2                           | Divide by 2   | 01              | 1_2             | No division                                        | Divide by 2             |

| 0 0011                                         | 4                           | Divide by 4   | 10              | 4_1             | Divide by 4                                        | No division             |

| 0 0101                                         | 8                           | Divide by 8   | 11              | 2_2             | Divide by 2                                        | Divide by 2             |

| 0 0111                                         | 16                          | Divide by 16  |                 |                 |                                                    |                         |

| 0 1001                                         | 32                          | Divide by 32  |                 |                 |                                                    |                         |

| 0 1011                                         | 64                          | Divide by 64  |                 |                 |                                                    |                         |

| 0 1101                                         | 128                         | Divide by 128 |                 |                 |                                                    |                         |

| 0 1111                                         | 256                         | Divide by 256 |                 |                 |                                                    |                         |

| 1 0001                                         | 512                         | Divide by 512 |                 |                 |                                                    |                         |

| sity of Florida, EEL 47<br>© Dr. Eric M. Schwa |                             |               |                 |                 |                                                    |                         |

9

University of Florida, EEL 4744 – File 00 © Dr. Eric M. Schwartz

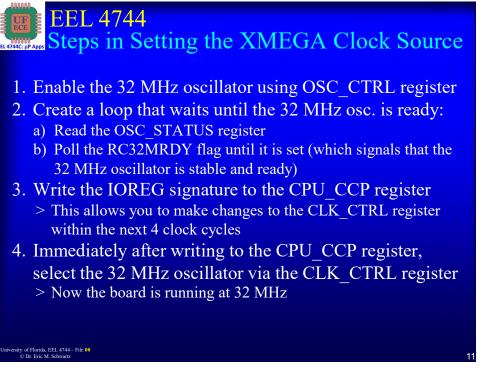

11

7

13

University of Florida, EEL 4744 – File 00 © Dr. Eric M. Schwartz